High Bandwith Memory

고대역메모리, 고대역폭메모리, 광대역폭 메모리는 삼성전자, AMD, SK하이닉스 3D스택방식의 DRAM을 위한 고성능 RAM 인터페이스를 말함.

폰노이만 구조

수학자이자 물리학자인 폰노이만과 다른 사람들이 1945년에 서술한 설명에 기반한 컴퓨터 아키텍쳐는 중앙처리장치(CPU), 메모리, 프로그램의 세 가지 요소로 구성되어 있음.

프로세서(CPU,GPU)는 메모리에서 데이터를 가져와서 처리를 할 때 데이터가 오는 속도가 프로세서의 처리속도를 못 따라가 병목이 생김. CPU, GPU의 속도가 점점 높아지기 때문에 데이터 전송 속도를 높이기 위해 Bandwith(데이터가 가는 길)을 넓힐 수 밖에 없음.

HBM의 구조

프로세서와 HBM은 2.5D로 연결되고 D램끼리는 3D로 연결됨. (삼성 i-cube)

후공정 기술이고 Advanced Package로 구현함. CPU, GPU, AP, SoC 쪽에서 TSV공법으로 연결하는 것을 생각했으나, 비표준화된 비메모리(3나노미터~5나노미터 사이즈)에 구멍을 뚫을 공간을 두고 설계하는 것이 쉽지 않아 메모리쪽으로 포커스를 맞추게 됨. 비메모리에 TSV를 뚫는 것은 쉽지 않음. D램에 TSV를 뚫어서 진행. 인터포저와 SiP(System in Package)라는 기판이 필요해짐.

장점: 사이즈 작아짐. 전력 소모 작아짐. 속도는 빨라짐.

→ 비메모리 2.5D + 메모리 3D

왜 실리콘 소재의 Interposer와 Substrate가 필요한가?

PCB(Package Substrate)는 최대한의 한계가 10 마이크로 미터 이하로 만들기 쉽지 않음. 현재는 30마이크로 미터 수준이고 다층기판으로 비아홀(via hole)로 연결됨. 50마이크로미터에서 25마이크로 미터 수준으로 만들기 위해서는 인터포저와 SiP이 필요함.

실리콘 인터포저: 웨이퍼 만드는 회사가 잘 만듬.

SiP: #삼성전기 #대덕전자 #심텍 #해성디에스

HBM은 어디에 사용되는가?

HBM은 원래 고성능 컴퓨터, 슈퍼컴퓨터에 사용되었지만 점점 대중화되고 있고 최근에는 인텔 사파이어 래피즈를 지원하고 모바일용도 곧 지원할 것으로 생각됨.

- 5G 통신은 Sub6(3.5GHz대역, 4G보다 50%빠름), mmWave(28GHz 대역, 20배 이상 빠름)으로 구성되고 미국에서 곧 상용화될 것으로 보이는데 이것을 사용할 경우 처리해야할 데이터가 증가됨.

- SiRi와 같은 Al가 처리하는 정보를 데이터센터를 이용하는 것이 아니라 스마트폰 자체에서 처리를 하게 되고 모바일용 HBM이 중요함. 최근에 애플 A 바이오닉 시리즈, 삼성전자 엑시노스 AP에 NPU(Neural Processing Unit)를 채택함. NPU성능이 올라가고 코어수가 많아지면 HBM이 더 필요한 상황임.

- 폴더블폰이 대중화되면 8K 지원되는 스마트폰이 출시될 것이고 해상도 처리를 위해서도 HBM이 필요함.

- 저가형 HBM은 PC 그래픽 카드 전용으로 개발 가능성도 있음. 실제 삼성전자는 최근 엔비디아와 협력을 많이 하고 있는데 고성능 GPU에 HBM2 적용을 검토하고 있음.

- 테슬라는 머신러닝을 활용하여 오직 카메라만으로 AI 기반 센싱을 하고 있음. 공급면에서 비용을 떨어뜨릴 수 있는 제조 경쟁력이 뒷받침이 되면 자율주행차는 물론 가전 제품에서도 HBM 적용은 시간 문제임.

병목을 넘어서 Bandwith 자체의 쇼티지가 심각해질 것임.

HBM은 어떤 방향으로 가고 있나?

2008년 AMD 제창(기술 아이디어만)→HBM(SK하이닉스)→HBM2(16년부터 삼성전자가 진입, 78% 속도 증가)→HBM3(SK하이닉스)

HBM3는 슈퍼컴퓨터용으로 초당 819GB로 속도가 빠르고 D램에 전달되는 에러를 스스로 보정함. HBM3에서 D램의 두께는 30마이크로 미터(A4 1/3 두께) 정도로 얇아져야 함. 그래서 Handdling 장비가 중요함.

#한미반도체 #이오테크닉스 #원익IPS(CVD장비) #케이씨텍(CMP장비) #인텍플렉스(3D검사) #고영

삼성전자는 HBM+PIM(processor in memory)

HBM 아래에 로직 Die를 하나 가져다 놓고 병목이 일어나지 않게 여기해서 일부 처리를 해 CPU나 GPU에 전송하는 기술

2021년 2월 자일링스 AI시스템에 삼성전자 HBM PIM 적용- 성능 2.5배 증가, 에너지 소모 60% 감소

https://n.news.naver.com/article/030/0002981248

삼성전자, 차세대 2.5D 패키지 기술 '에이치-큐브' 개발

삼성전자가 새로운 2.5D 패키지 기술 '에이치-큐브(H-Cube)'를 선보였다. 에이치큐브는 반도체 크기를 줄이면서 차세대 메모리칩(HBM)을 여러개 집적해 전력 효율을 극대화했다. 삼성전자는 삼성전

n.news.naver.com

HBM 시장이 커지면 어떤 회사가 수혜를 볼 수 있을까?

#이오테크닉스

미세드릴(레이저 장비) 회사. 실리콘 인터포저, 기판, SiP 쪽에 signal이 만아지면 더 많은 회로를 넣어야 함. 기존 CO2 드릴은 50마이크로 미터 수준의 드릴인데, UV 레이저 드릴은 25마이크로 미터 수준의 드릴 가능→ASP 단가 상승, 마진도 좋아짐.

#한미반도체

기존 주력 장비인 VP(vision placement)와 EMI차폐 장비는 여전히 좋고 chip to chip 커뮤니케이션이 많아지기 때문에 본딩 쪽이 커질 가능성이 있음. TC본더는 HBM3를 위해 이미 SK하이닉스향 장비 수주를 함. SiP가 되면 두께를 얇게 해야하고 갈아내는 장비인 스트립 그라인더의 전망 역시 좋아짐. 이외에 카메라 쪽 검사 장비도 유망함.

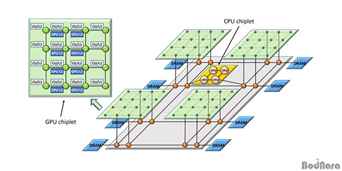

Chiplet?

예전에는 코어를 여러 개 쓰더라도 SoC 원칩으로 해서 IP블록을 만듬. 요즘에는 프로세서에 코어가 너무 적용되고, 다이크기도 많이 커져서 로스 비용이 증가됨. 그래서 고성능 코어와 저성능 코어를 함께 탑재 함.

인텔 엘더레이크 (10 나노미터 CPU,PC용)역시 빅리틀 구조로 상대적으로 전력 소모가 적은 저성능 코어 (LITTLE)들과 전력 소모가 많은 고성능 프로세서 코어(BIG)을 함께 탑재함. 이것은 ARM(RISC기반) 기술이고 애플 m1도 빅리틀 구조임.

고성능 코어는 5나노 공정으로 만들어 TSMC에 주문하고 저성능 코어는 14나노 공정으로 글로벌 파운드리에 주문함.

→파운드리를 이원화해도 되는 상황.

코어를 각각 가지고 와서 die on하여 2.5D에 부착함.

메모리는 3D로 쌓은 후 TSV로 연결함.

Chiplet 구조로 가면서 기판이 많이 필요해지고 SiP나 인터포저가 많이 필요해짐.

'산업 분석' 카테고리의 다른 글

| [2차전지]테슬라 CTC, 허니콤 구조 (0) | 2021.11.19 |

|---|---|

| [2차전지]각형배터리 분석 (0) | 2021.11.17 |

| [모빌리티]UAM 산업 자료 수집 중 (0) | 2021.11.17 |

| [반도체]반도체 기판(Package Substrate, PCB) (0) | 2021.11.17 |

| [2차전지]배터리 산업군 투자 가이드 (0) | 2021.11.16 |