PCB는 왜 나오게 되었나?

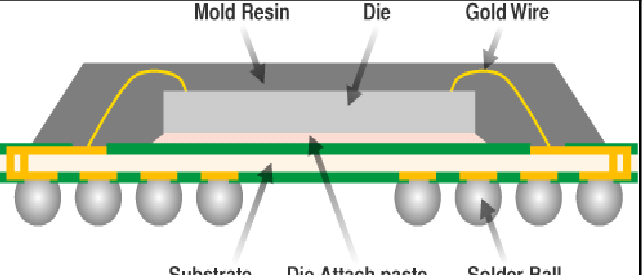

원래 반도체 구조는 리드프레임+와이어 본딩으로 구성이 되어 있었음.

->I/O가 200개 이상이 넘어가면 한계가 있어, 핀수의 제한이 있음.

그래서 Ball Grid Array(BGA, 집적 회로에서 사용되는 표면 실장 패키지의 한 종류)방식으로 바뀜.

종류는?

1) FBGA(Fine =pitch Ball Grid Array)

PCB 기판의 밑면에 리드를 대신하는 SOLER BALL Array 를 갖는 표면 신장형 패키지. Substrate 처음 쓰임. D램, 낸드 플레시에 쓰임.

기판 크기가 크고 Die는 작음 I/O 숫자가 많음. 데이터 손실은 줄이고 전력 효율성은 높임.

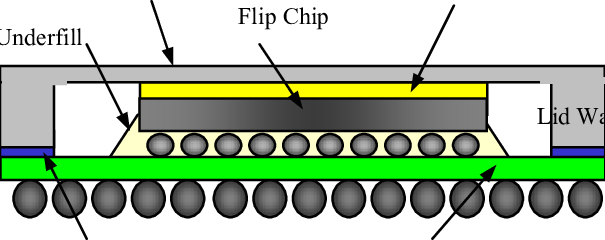

2000년대 신기술 WLP(Wafer Level Packaging), FC(Flip- chip)

Die 크기가 Substrate 대비 80%이상 FC-CSP. 80%이하 FC-BGA

Die에 비해 기판이 크면 I/O 수가 많음.

2010년대부터

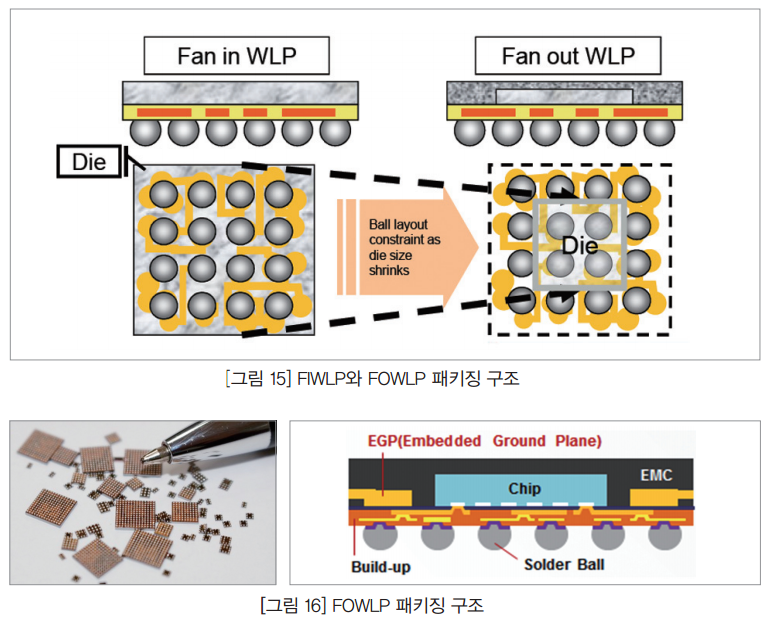

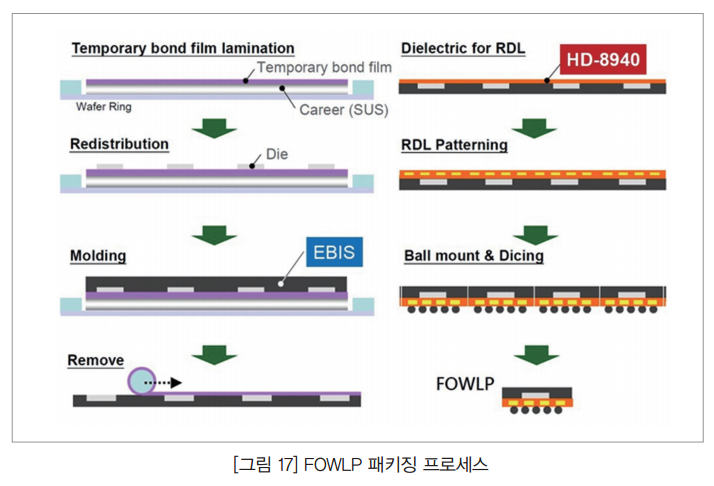

Tsmc제외 삼성은 FC-CSP를 씀. Tsma는 애플 AP로 Fo-WLP를 씀.

(Fo-WLP는 원래 있었는데 독일 인피니언사가 개발한 것으로 I/O가 600개, Tsmc는 I/O를 1000개 구현- 고성능)

FC-BGA는 CPU, GPU, TPU, M1에 사용됨. 상반기 가격이 40% 증가, 서버용은 이비덴, 신코덴키 독점, 클라우드 기업향 수요가 증가되고 있음. 인텔향 삼성전지, 대덕전자에게 물량 보전 투자, PC용 삼성전기도 가능. FC-BGA는 전체 기판 중 비중 47% 앞으로 더 많이 쓰일 것임. Aip(Antena un Package- 5G,mmWave) 시장은 성장하고 있음.

Aip의 시장 규모는 1조. 성장성이 큼.

5G, Sub6-mmWave: 3.5GHz, 28Ghz, 데이터 속도가 빠르고 직진성이 강함. 주파수 감쇠 효과 큼.

Aip는 안테나 트랜시버 IC같이 붙여 패키징. Aip도 PCB가 필요함: 삼성전기+LG이노텍 장악

[반도체 8대 공정] 9탄, 외부환경으로부터 반도체를 보호하는 패키징 (Packaging) 공정 – 삼성반도

반도체 칩은 제품으로 출하되기 전 양품, 불량품을 선별하기 위한 테스트를 거치게 됩니다. 지난 시간에는 웨이퍼 완성 단계에서 이루어지는 테스트 ‘EDS 공정(Electrical Die Sorting)’에 대해 알아

www.samsungsemiconstory.com

'산업 분석' 카테고리의 다른 글

| [2차전지]테슬라 CTC, 허니콤 구조 (0) | 2021.11.19 |

|---|---|

| [2차전지]각형배터리 분석 (0) | 2021.11.17 |

| [모빌리티]UAM 산업 자료 수집 중 (0) | 2021.11.17 |

| [2차전지]배터리 산업군 투자 가이드 (0) | 2021.11.16 |

| [반도체] HBM(High Bandwith Memory) (0) | 2021.11.12 |